Overview

WriteupVideo Overview

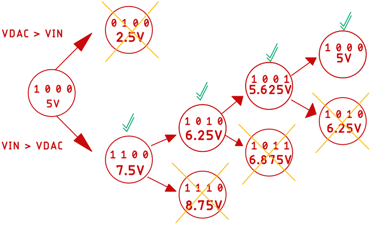

The successive approximation register (SAR) analog-to-digital converter (ADC) approximates an analog signal in several steps, starting with the most significant bit (MSB) and working down to the least significant bit (LSB). A single comparator, with its reference voltage controlled by an R/2R DAC, determines each bit in sequence. A sample and hold circuit stores the voltage during the conversion process, ensuring accurate measurements. The SAR ADC operates efficiently using a binary search algorithm, allowing some implementations to sample at rates in excess of 10 MHz.

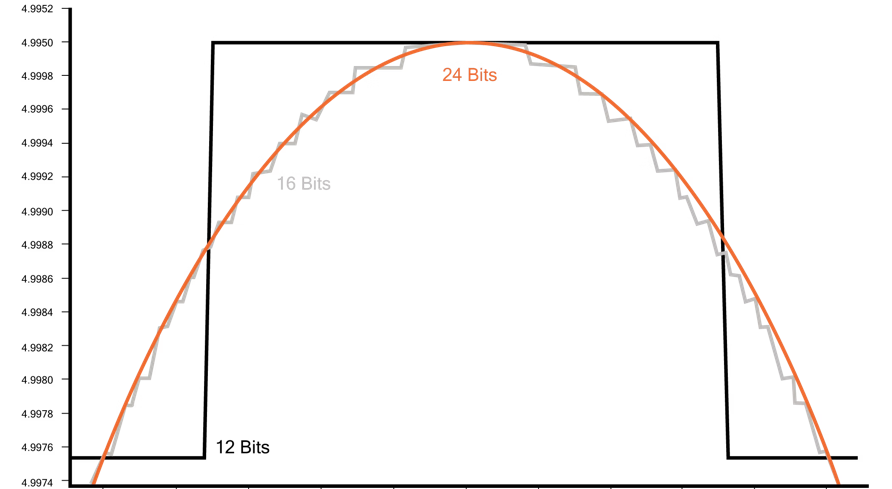

Since the SAR algorithm results in a digital approximation of the original voltage of finite resolution, the generated approximation is not a smooth, continuous function, even if the original is.